SPI腳座的迷思

按照當初SPI FALSH的少腳位的確給了許多IC設計公司和電子產品製造公司一個不錯的降低成本機會,

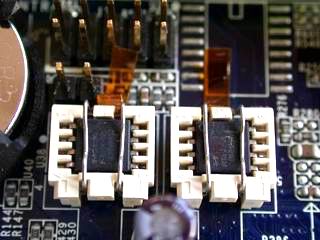

但是卻也給研發人員在開發階段產生許多不便!是的,沒有共通的開發用轉接腳座,

每一家廠商提出的解決方式和真正洗出來的公板都有不同的轉接方式或針腳定義,

市面上的轉接腳座也因應SPI FLASH的小包裝而產生使用上極為不便的困擾,真正的降低成本了嗎?

照我個人觀點來看,很多意外的成本支出是在後段出貨後的維護服務所產生。舉主機板的例子來看,

出貨後如果因為玩家升級BIOS失敗,開不了機了,也無法再利用磁碟機開機來更新BIOS,

SPI FLASH已經焊死在上面了耶!看來不解焊拔下來燒錄再焊回去是無解了,以前ISA和LPC的FLASH都還有用一個腳座,

真的不幸更新失敗還可以直接拔下來燒錄好再裝回去,現在可就沒辦法了,送回原廠去更新的話是要花點小錢!

一方面浪費了使用者的時間!另外一方面卻也增加維修人員的LOADING,SOP8也是需要特殊的腳座才能燒錄,

不然還得另外投資ISP燒錄工具。我實在很好奇為什麼不用DIP包裝的SPI FLASH呢?

這種從以前通用至今的DIP8包裝的腳座也不大啊!

使用者還可以自己拔下來找台老燒錄器更新一下支援的IC程式資料庫來燒錄就可以囉!

維護站舊的的燒錄設備也都可以沿用不會浪費啦!開發階段模擬器要上板子也就方便多啦!

所以個人強烈建議如果還在開發階段,記得多LAY一個DIP8的腳座會比較好些!

不然開發韌體的工程師就苦命一點,只有8 PIN而已,自己跳線比較快!

但是卻也給研發人員在開發階段產生許多不便!是的,沒有共通的開發用轉接腳座,

每一家廠商提出的解決方式和真正洗出來的公板都有不同的轉接方式或針腳定義,

市面上的轉接腳座也因應SPI FLASH的小包裝而產生使用上極為不便的困擾,真正的降低成本了嗎?

照我個人觀點來看,很多意外的成本支出是在後段出貨後的維護服務所產生。舉主機板的例子來看,

出貨後如果因為玩家升級BIOS失敗,開不了機了,也無法再利用磁碟機開機來更新BIOS,

SPI FLASH已經焊死在上面了耶!看來不解焊拔下來燒錄再焊回去是無解了,以前ISA和LPC的FLASH都還有用一個腳座,

真的不幸更新失敗還可以直接拔下來燒錄好再裝回去,現在可就沒辦法了,送回原廠去更新的話是要花點小錢!

一方面浪費了使用者的時間!另外一方面卻也增加維修人員的LOADING,SOP8也是需要特殊的腳座才能燒錄,

不然還得另外投資ISP燒錄工具。我實在很好奇為什麼不用DIP包裝的SPI FLASH呢?

這種從以前通用至今的DIP8包裝的腳座也不大啊!

使用者還可以自己拔下來找台老燒錄器更新一下支援的IC程式資料庫來燒錄就可以囉!

維護站舊的的燒錄設備也都可以沿用不會浪費啦!開發階段模擬器要上板子也就方便多啦!

所以個人強烈建議如果還在開發階段,記得多LAY一個DIP8的腳座會比較好些!

不然開發韌體的工程師就苦命一點,只有8 PIN而已,自己跳線比較快!